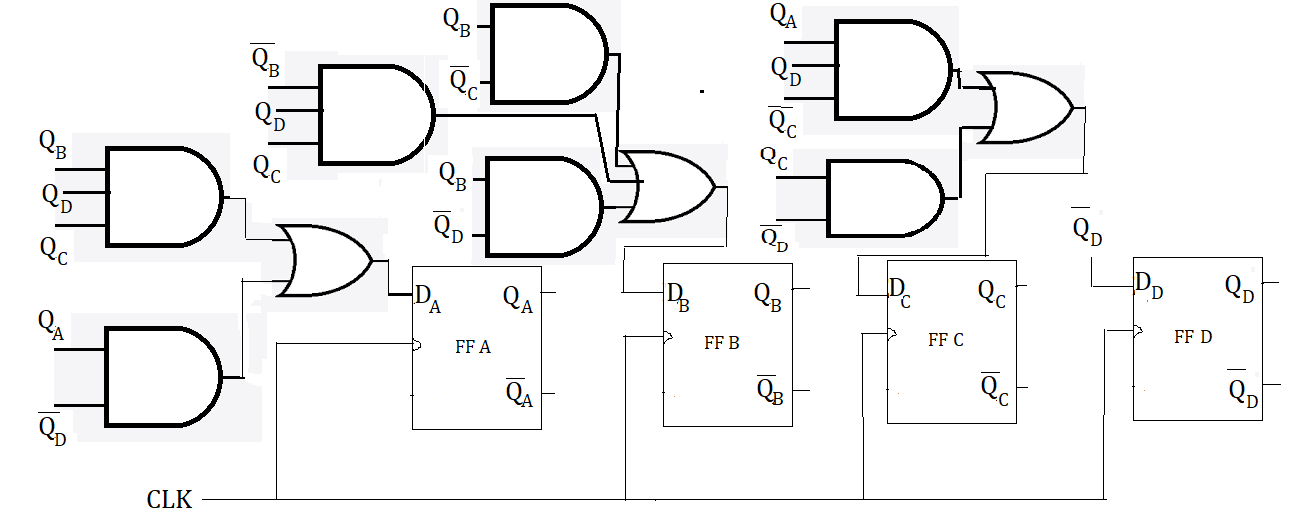

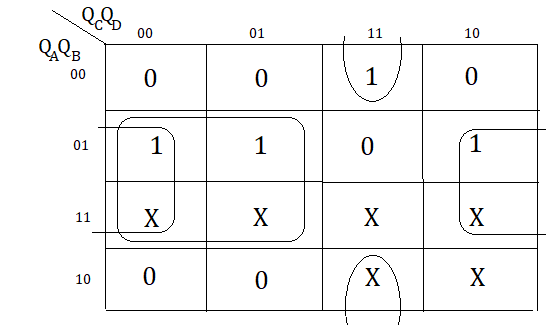

How to design a mod 10 counter using JK Flip-Flops. with the clock pulse for the counter will be generated using a 555 timer as an astable multivibrator. The output must be

Design MOD-10 Synchronous Up Counter Using JK Flip Flop | MOD 10 Counter Using JK Flip Flop - YouTube

Design mod 10 Synchronous Counter using JKFF - Sequential Logic Circuit - Digital Circuit Design - YouTube

Design MOD-10 asynchronous UP counter using positive edge triggered FF with timing diagram. Can I use a JK FF in place of edge triggered FF? - Quora

Design MOD 10 Synchronous Down Counter Using T Flip Flop | MOD 10 Counter Using T Flip Flop - YouTube

How to design a mod 10 counter using JK Flip-Flops. with the clock pulse for the counter will be generated using a 555 timer as an astable multivibrator. The output must be

Design MOD-10 Synchronous Up Counter Using JK Flip Flop | MOD 10 Counter Using JK Flip Flop - YouTube

Mod 10 Synchronous counter using D flip flop | Synchronous counter design using DFF| Mod 10 Counter - YouTube

Design MOD-10 asynchronous UP counter using positive edge triggered FF with timing diagram. Can I use a JK FF in place of edge triggered FF? - Quora

How to design a mod 10 counter using JK Flip-Flops. with the clock pulse for the counter will be generated using a 555 timer as an astable multivibrator. The output must be

How to design a mod 10 counter using JK Flip-Flops. with the clock pulse for the counter will be generated using a 555 timer as an astable multivibrator. The output must be

Design MOD-10 Synchronous Up Counter Using JK Flip Flop | MOD 10 Counter Using JK Flip Flop - YouTube

How to design a mod 10 counter using JK Flip-Flops. with the clock pulse for the counter will be generated using a 555 timer as an astable multivibrator. The output must be

Design mod-10 synchronous counter using JK Flip Flops.Check for the lock out condition.If so,how the lock-out condition can be avoided? Draw the neat state diagram and circuit diagram with Flip Flops.